S1C31D51/50 (rev2.02)

#### **32-bit Single Chip Microcontroller**

- Arm® 32-bit RISC CPUcore Cortex®-M0+

- Embedded 192K bytes Flash memory (Program & Sound ROM), 10K(D51)/8K(D50) bytes RAM

- Enable to output voice guidance on a buzzer in addition to a speaker

- "Voice/Audio Play" (2ch mixing play, Voice Speed Conversion w/o CPU resource)

- "Self Memory Check" w/o CPU resource

#### DESCRIPTIONS

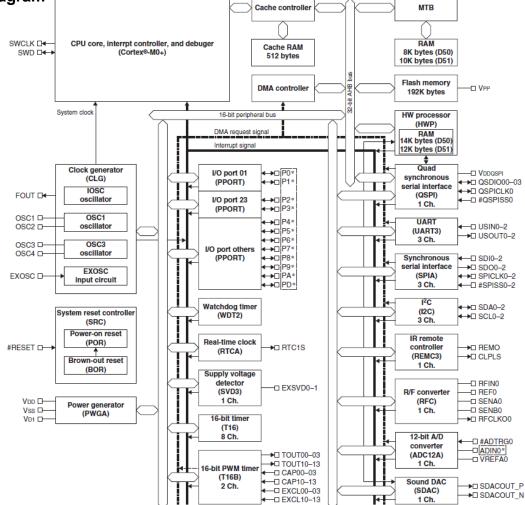

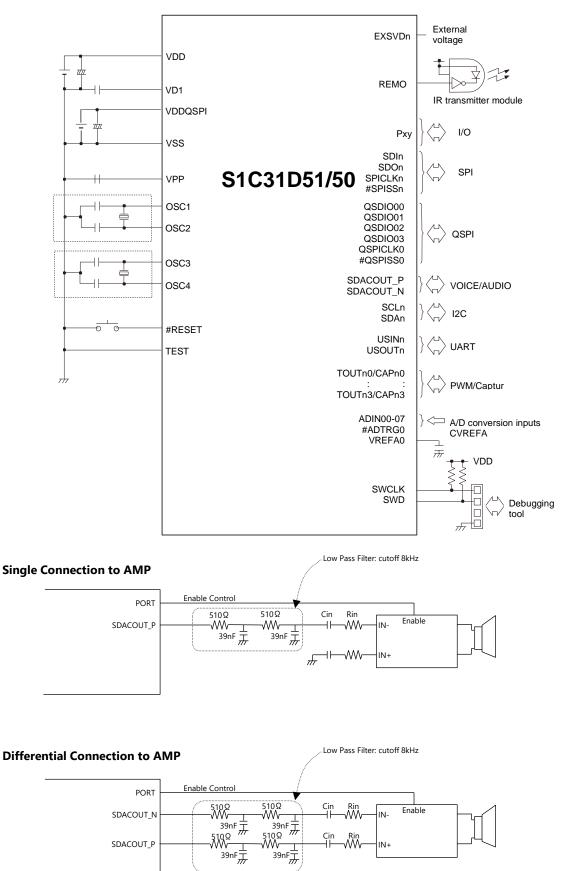

The S1C31D51/D50 is a 32-bit Arm® Cortex®-M0+ MCU which integrates a specific hardware block called the HW Processor. Normally, the buzzer does not provide sufficient voice quality and sound pressure, but our newly developed algorithm allows the buzzer to play the voice, and even devices that could not be equipped with a speaker and voice guidance can generate an error or warning, and can improve usability for the end user.

The HW Processor can perform 2ch Voice/Audio Play, Voice Speed Conversion, and Self Memory Check without using any CPU resource, and the S1C31D51/D50 is suitable for home electronics, white goods, and battery-based products which require voice and audio playback.

In addition, the audio playback format uses a high-compression, high-quality sound algorithm, which makes it possible to install multiple languages.

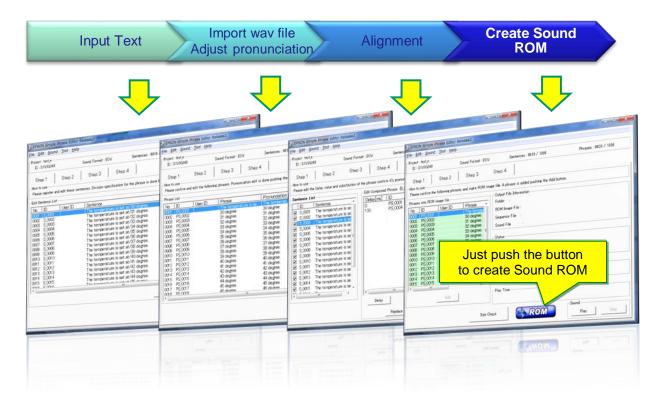

Furthermore, the EPSON Voice Creation PC tool makes development without studio recording easy.

#### ■ FEATURES

| Model                                                   | S1C31D50                                                                                | S1C31D51                                                               |  |  |  |  |  |  |  |

|---------------------------------------------------------|-----------------------------------------------------------------------------------------|------------------------------------------------------------------------|--|--|--|--|--|--|--|

| CPU                                                     |                                                                                         |                                                                        |  |  |  |  |  |  |  |

| CPU core                                                | Arm® 32-bit RISC CPU core Cortex <sup>®</sup> -M0+                                      |                                                                        |  |  |  |  |  |  |  |

| Other                                                   | Serial-wire debug ports (SW-DP) and a micro to                                          | race buffer (MTB) included                                             |  |  |  |  |  |  |  |

| Embedded Flash memory                                   |                                                                                         |                                                                        |  |  |  |  |  |  |  |

| Capacity                                                | 192K bytes (for both instructions and data)                                             |                                                                        |  |  |  |  |  |  |  |

| Erase/program count                                     | 1,000 times (min.) * When being programmed I                                            | 000 times (min.) * When being programmed by the dedicated flash loader |  |  |  |  |  |  |  |

| Other                                                   | On-board programming function                                                           |                                                                        |  |  |  |  |  |  |  |

|                                                         | Flash programming voltage can be generated i                                            | nternally.                                                             |  |  |  |  |  |  |  |

| Embedded RAMs                                           |                                                                                         |                                                                        |  |  |  |  |  |  |  |

| General-purpose RAM                                     | 8K bytes + 14K bytes (when HW Processor is not active)                                  | 10K bytes + 12K bytes (when HW Processor is not active)                |  |  |  |  |  |  |  |

| HW Processor                                            |                                                                                         |                                                                        |  |  |  |  |  |  |  |

| Voice Audio Play FUNCTION                               |                                                                                         |                                                                        |  |  |  |  |  |  |  |

| Voice/Audio Algorithm                                   | EPSON high quality & High compress algorithm                                            | n                                                                      |  |  |  |  |  |  |  |

| Play channels                                           | 2ch mixing support (example: Ch0: voice, Ch1:                                           | BGM)                                                                   |  |  |  |  |  |  |  |

| Sampling Frequency                                      | 15.625kHz, (suitable for background music + V                                           | oice play)                                                             |  |  |  |  |  |  |  |

| Bitrate                                                 | 16/24/32/40 kbps                                                                        |                                                                        |  |  |  |  |  |  |  |

| Voice Speed Conversion                                  | 75% - 125% (5% step)                                                                    |                                                                        |  |  |  |  |  |  |  |

| Self Memory Check FUNCTION                              |                                                                                         |                                                                        |  |  |  |  |  |  |  |

| On Chip RAM Check                                       | W/R Check, MARCH-C                                                                      |                                                                        |  |  |  |  |  |  |  |

| On Chip Flash check                                     | Checksum, CRC                                                                           |                                                                        |  |  |  |  |  |  |  |

| External SPI-Flash Check                                | Checksum, CRC                                                                           |                                                                        |  |  |  |  |  |  |  |

| Sound DAC                                               | •                                                                                       |                                                                        |  |  |  |  |  |  |  |

| Sampling Frequency                                      | 15.625kHz                                                                               |                                                                        |  |  |  |  |  |  |  |

| External Differential Circuit Spea                      | ker DAC/Electromagnetic Buzzer DAC/Piezoe                                               | lectric buzzer DAC                                                     |  |  |  |  |  |  |  |

| Sampling Frequency<br>(A16bit PWM timer (T16B) is used) | (not supported)                                                                         | 15.625kHz                                                              |  |  |  |  |  |  |  |

| Serial interfaces                                       |                                                                                         |                                                                        |  |  |  |  |  |  |  |

| UART (UART3)                                            | 3 channels                                                                              |                                                                        |  |  |  |  |  |  |  |

|                                                         | Baud-rate generator included, IrDA1.0 support                                           |                                                                        |  |  |  |  |  |  |  |

|                                                         | Open drain output, signal polarity, and baud ra                                         |                                                                        |  |  |  |  |  |  |  |

|                                                         | Infrared communication carrier modulation out                                           | put function                                                           |  |  |  |  |  |  |  |

| Synchronous serial interface (SPIA)                     | 3 channels                                                                              |                                                                        |  |  |  |  |  |  |  |

|                                                         | 2 to 16-bit variable data length                                                        |                                                                        |  |  |  |  |  |  |  |

|                                                         | The 16-bit timer (T16) can be used for the bau                                          | d-rate generator in master mode.                                       |  |  |  |  |  |  |  |

| Quad synchronous serial interface                       | 1 channel                                                                               |                                                                        |  |  |  |  |  |  |  |

| (QSPI)                                                  | Supports single, dual, and quad transfer mode                                           |                                                                        |  |  |  |  |  |  |  |

|                                                         | Low CPU overhead memory mapped access n<br>flash memory with XIP (eXecute-In-Place) mod | node that can directly read data from the external e.                  |  |  |  |  |  |  |  |

| I <sup>2</sup> C (I2C)                                  | 3 channels                                                                              |                                                                        |  |  |  |  |  |  |  |

|                                                         | Baud-rate generator included                                                            |                                                                        |  |  |  |  |  |  |  |

| Model                                                                                                                                                                                                                                                                                                                                                                                                                                | S1C31D50 S1C31D51                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DMA Controller (DMAC)                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Number of channels                                                                                                                                                                                                                                                                                                                                                                                                                   | 4 channels                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Data transfer bus                                                                                                                                                                                                                                                                                                                                                                                                                    | Memory to memory, memory to peripheral, and peripheral to memory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Transfer mode                                                                                                                                                                                                                                                                                                                                                                                                                        | Basic, ping-pong, scatter-gather                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| DMA trigger source                                                                                                                                                                                                                                                                                                                                                                                                                   | UART3, SPIA, QSPI, I2C, T16B, ADC12A, and software                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Clock generator (CLG)                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| System clock source                                                                                                                                                                                                                                                                                                                                                                                                                  | 4 sources (IOSC/OSC1/OSC3/EXOSC)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| System clock frequency                                                                                                                                                                                                                                                                                                                                                                                                               | VD1 voltage mode = mode0: 16 MHz (max.)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| (operating frequency)                                                                                                                                                                                                                                                                                                                                                                                                                | VD1 voltage mode = mode1: 1.8 MHz (max.)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| IOSC oscillator circuit                                                                                                                                                                                                                                                                                                                                                                                                              | VD1 voltage mode = mode0: 8/2/1 MHz (typ.) software selectable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| (boot clock source)                                                                                                                                                                                                                                                                                                                                                                                                                  | VD1 voltage mode = mode1: 1.9/0.9 MHz (typ.) software selectable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                      | 10 µs (max.) starting time (time from cancelation of SLEEP state to vector table read by the CPU                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| OSC1 oscillator circuit                                                                                                                                                                                                                                                                                                                                                                                                              | 32.768 kHz (typ.) crystal oscillator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                      | 32kHz (typ.) embedded oscillator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                      | Oscillation stop detection circuit included                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| OSC3 oscillator circuit                                                                                                                                                                                                                                                                                                                                                                                                              | 16 MHz (max.) crystal/ceramic oscillator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                      | 16/8/4MHz (typ) embedded oscillator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| EXOSC clock input                                                                                                                                                                                                                                                                                                                                                                                                                    | 16 MHz (max.) square or sine wave input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Other                                                                                                                                                                                                                                                                                                                                                                                                                                | Configurable system clock division ratio                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                      | Configurable system clock used at wake up from SLEEP state                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                      | Operating clock frequency for the CPU and all peripheral circuits is selectable.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| I/O port (PPORT)                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

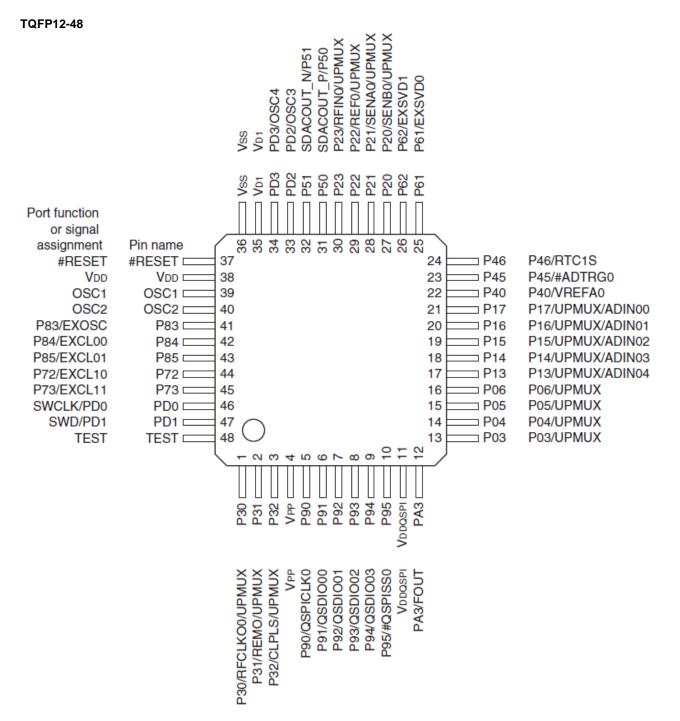

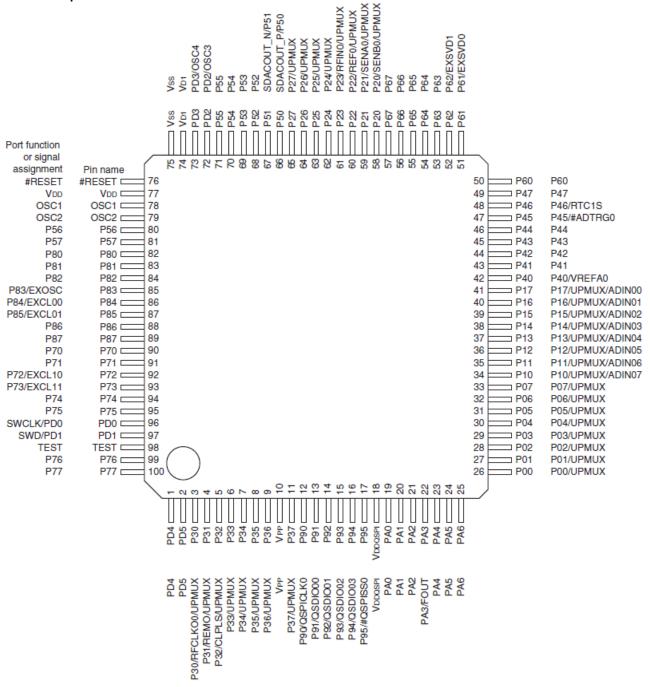

|                                                                                                                                                                                                                                                                                                                                                                                                                                      | PKG48pin : 39bit(max.)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

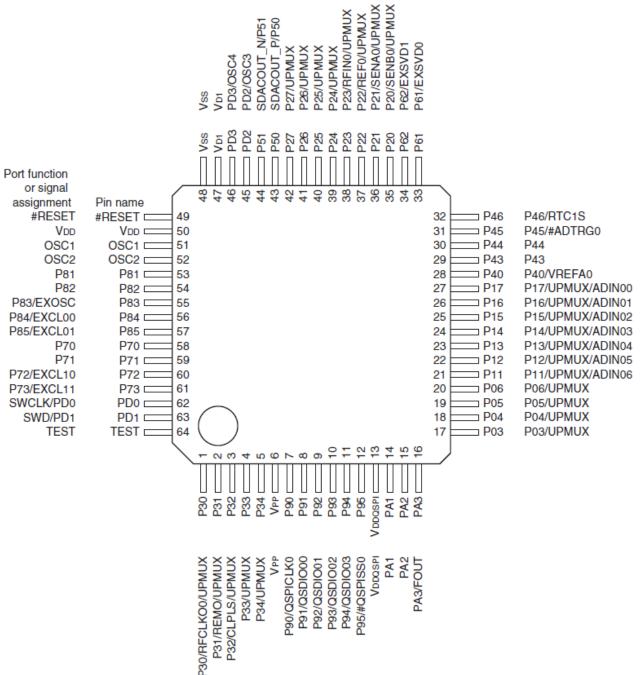

| oorts                                                                                                                                                                                                                                                                                                                                                                                                                                | PKG64pin : 55bit(max.)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

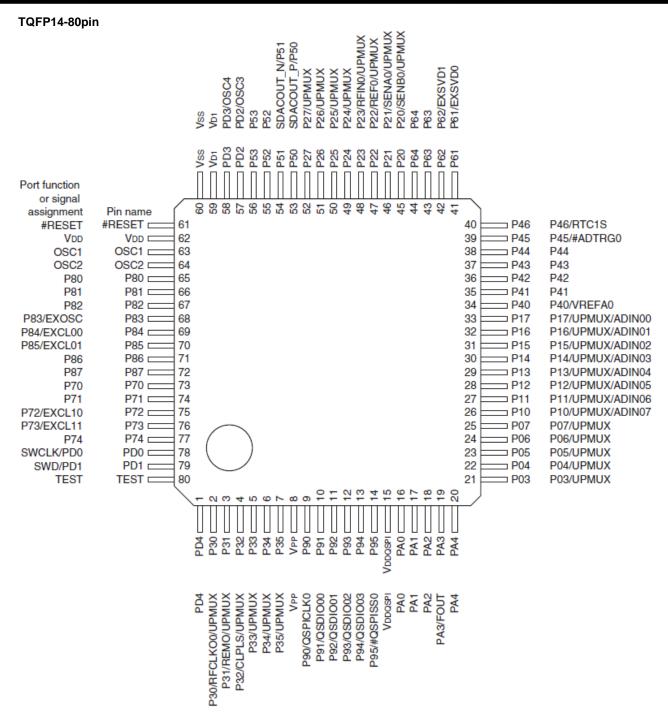

|                                                                                                                                                                                                                                                                                                                                                                                                                                      | PKG80pin : 71bit(max.)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                      | PKG100pin : 91bit (max.)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                      | Pins are shared with the peripheral I/O.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Number of input interrupt ports                                                                                                                                                                                                                                                                                                                                                                                                      | PKG48pin : 33bit(max.)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                      | PKG64pin : 49bit(max.)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                      | PKG80pin : 65bit(max.)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                      | PKG100pin : 85bit (max.)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Number of ports that support                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| universal port multiplexer (UPMUX)                                                                                                                                                                                                                                                                                                                                                                                                   | PKG64pin : 24bit(max.)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                      | PKG80pin : 27bit(max.)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                      | PKG100pin : 32bit (max.)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                      | A peripheral circuit I/O function selected via software can be assigned to each port.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Timers                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Watchdog timer (WDT2)                                                                                                                                                                                                                                                                                                                                                                                                                | Generates NMI or watchdog timer reset.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                      | Programmable NMI/reset generation cycle                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Real-time clock (RTCA)                                                                                                                                                                                                                                                                                                                                                                                                               | 128–1 Hz counter, second/minute/hour/day/day of the week/month/year counters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Real-time Clock (RTCA)                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                      | Theoretical regulation function for 1-second correction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                      | Alarm and stopwatch functions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 16-bit timer (T16)                                                                                                                                                                                                                                                                                                                                                                                                                   | 8 channels                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                      | Generates the SPIA and QSPI master clocks, and the ADC12A operating clock/ trigger signal.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 16-bit PWM timer (T16B)                                                                                                                                                                                                                                                                                                                                                                                                              | 2 channels                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                      | Event counter/capture function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                      | PWM waveform generation function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                      | Number of PWM output or capture input ports: 4 ports/channel                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Supply voltage detector (SVD3)                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Number of channels                                                                                                                                                                                                                                                                                                                                                                                                                   | 1 channel                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Detection voltage                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                      | VDD or an external voltage (2 external detection ports are available )                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                      | VDD or an external voltage (2 external detection ports are available.)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Detection level                                                                                                                                                                                                                                                                                                                                                                                                                      | VDD: 28 levels (1.8 to 5.0 V)/external voltage: 32 levels (1.2 to 5.0 V)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Detection level                                                                                                                                                                                                                                                                                                                                                                                                                      | VDD: 28 levels (1.8 to 5.0 V)/external voltage: 32 levels (1.2 to 5.0 V)<br>Intermittent operation mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Detection level<br>Other                                                                                                                                                                                                                                                                                                                                                                                                             | VDD: 28 levels (1.8 to 5.0 V)/external voltage: 32 levels (1.2 to 5.0 V)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Detection level<br>Other<br>12-bit A/D converter (ADC12A)                                                                                                                                                                                                                                                                                                                                                                            | VDD: 28 levels (1.8 to 5.0 V)/external voltage: 32 levels (1.2 to 5.0 V)<br>Intermittent operation mode<br>Generates an interrupt or reset according to the detection level evaluation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |